Tin mới & Sự kiện

AI chuyên dùng vi mạch (ASIC/GPU/FPGA) giao diện mạng Ethernet - 400G/800G thử nghiệm và xác minh.

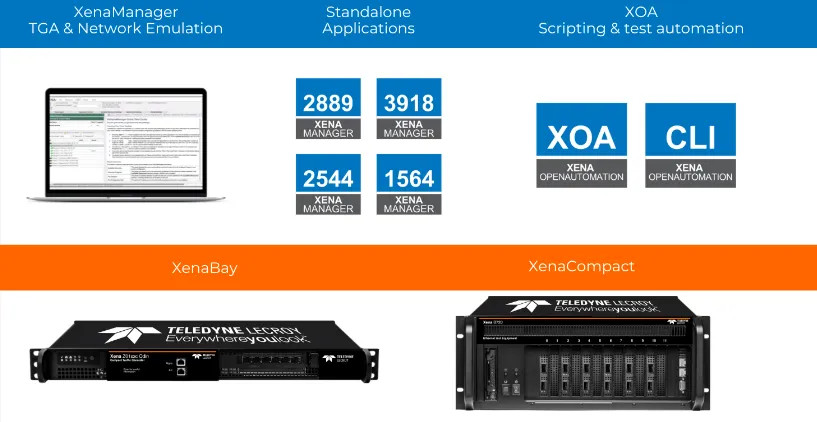

XENA Networks và xác minh sản phẩm Ethernet của họ một cách nhanh chóng và hiệu quả, tăng tốc việc tung ra thị trường sản phẩm thế hệ mới của họ. ển mạch/định tuyến và PHY/SERDES, nhưng trong những năm gần đây, nhu cầu mới đã xuất hiện từ các nhà sản xuất chip công nghệ mới như GPU/DPU/XPU.

Cùng với sự phổ biến của các mô hình AI lớn và các cụm lớn, việc thử nghiệm và xác minh kỹ thuật mạng Ethernet tốc độ cao giữa c ác vi mạch AI chuyên dụng là điều quan trọng. tôi hỗ trợ:

- Giao diện và chế độ tốc độ thử nghiệm XENA: 400G/800G

- Xác minh và thử nghiệm hiệu suất lớp vật lý mạng Ethernet: FEC/AN-LT/PRBS/Rx Taps

- Mô phỏng ảnh hưởng tiêu cực trên mạng Ethernet: Độ rung trễ/Dao động đường truyền

![]()

Giao diện và chế độ tốc độ thử nghiệm:

- Giao diện gốc QSPF-DD: 112Gb/S 56Gb/S

- Giao diện gốc OSPF: 112Gb/S 56Gb/S

- Cổng phân phối HCB:

800G: 8*112G/Lane

400G: 4112G/Lane và 856G/Lane

200G: 2112G/Lane và 456G/Lane

100G: 1112G/Lane và 256G/Lane

50G: 1*56G/Lane

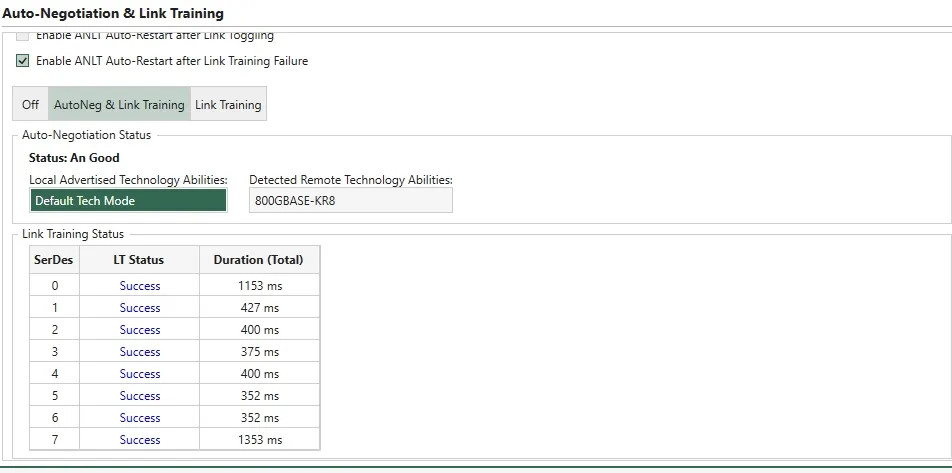

Thử nghiệm và xác minh hiệu suất lớp vật lý:

- Thử nghiệm áp lực không kết hợp (PRBS)

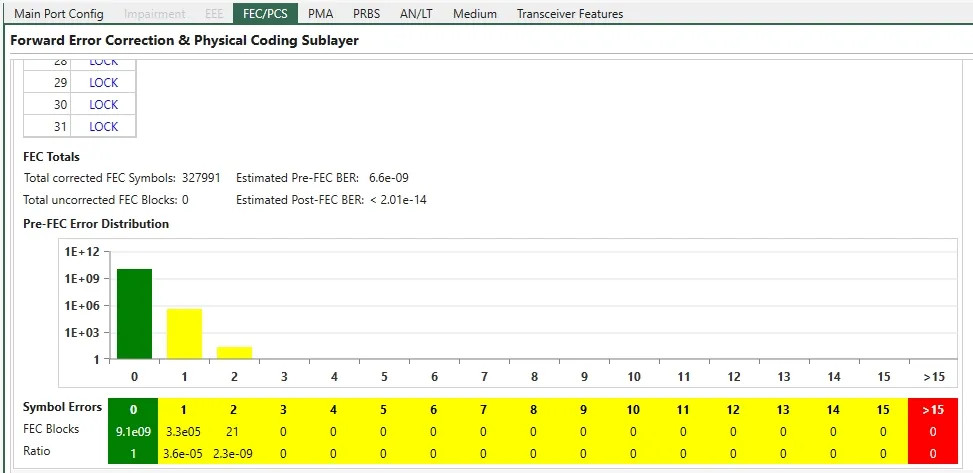

- Đánh giá lượng dư thừa có thể được sửa lỗi ở cấp độ vật lý (RS-FEC)

- Tự điều chỉnh cổng và học đường dẫn một cách tự động (AN-LT)

- Thử nghiệm ghi/đọc bộ nhớ tạm qua giao tiếp I2C

- Xem xét tính toàn vẹn của tín hiệu (SIV)

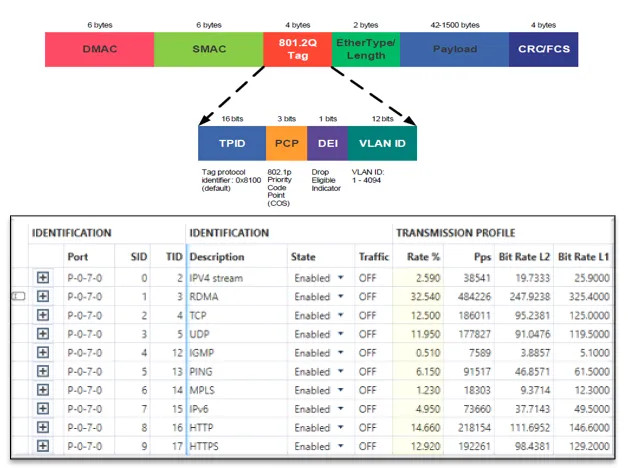

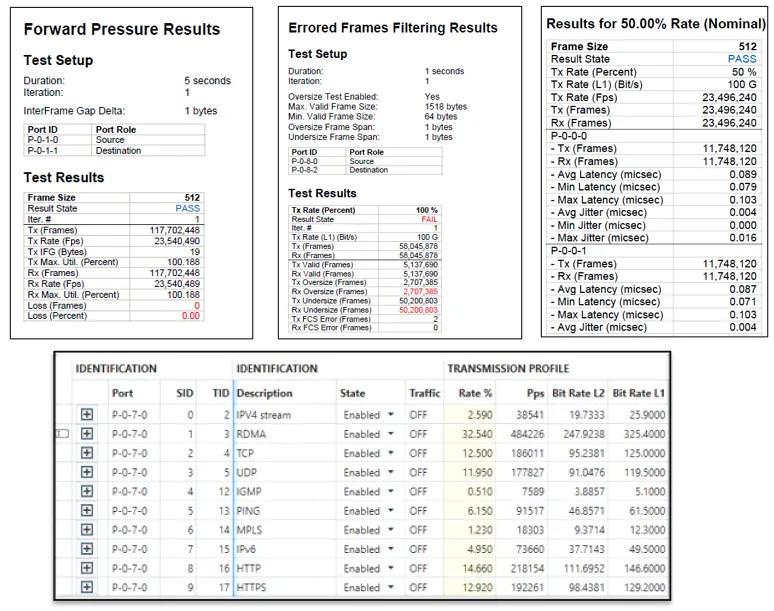

Thử nghiệm hiệu suất lưu lượng mạng Ethernet:

- Chế độ đa dòng

- Mô phỏng các giao thức MAC/IP/TCP/RDMA khác nhau

- Tốc độ toàn bộ dòng: 64/1518/9000 Byte

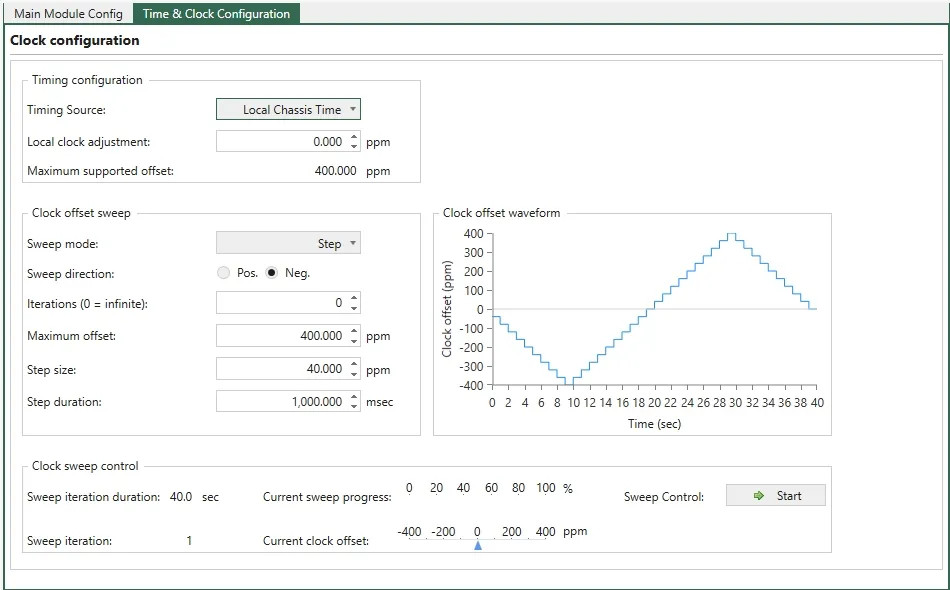

- Hỗ trợ điều chỉnh lệch tần số của đồng hồ với khoảng cách cực rộng ±400ppm

- Cung cấp bộ kiểm tra hiệu suất theo tiêu chuẩn RFC

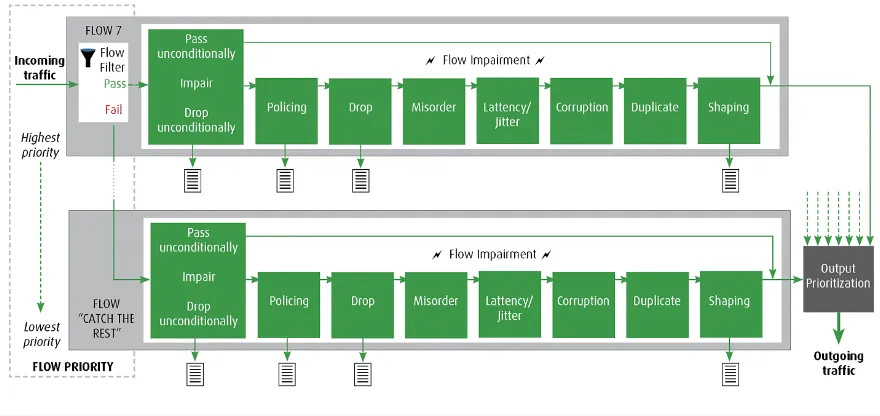

Mô phỏng áp lực tiêu cực trên mạng Ethernet:

- Thử nghiệm tần suất cao của việc mất kết nối vật lý (Link Flap)

- Chèn mã lỗi ở tầng PMA/PCS

- Tạo độ rung và chèn lỗi vào gói tin

- Chèn lỗi FCS/Checksum Error

Đặc điểm sản phẩm Valkyrie:

- Sản phẩm kết hợp thẻ cắm trong hộp

- Cung cấp phần mềm điều khiển đồ họa Window - Bass GUI

- Cung cấp bộ công cụ phát triển API cho việc phát triển lần thứ hai